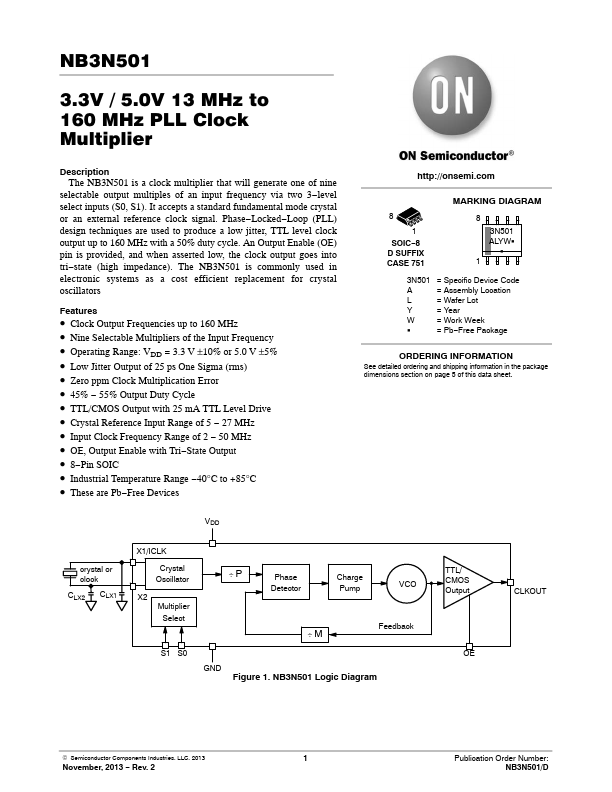

NB3N501 Description

The NB3N501 is a clock multiplier that will generate one of nine selectable output multiples of an input frequency via two 3−level select inputs (S0, S1). It accepts a standard fundamental mode crystal or an external reference clock signal. Phase−Locked−Loop (PLL) design techniques are used to produce a low jitter, TTL level clock output up to 160 MHz with a 50% duty cycle.

NB3N501 Key Features

- Clock Output Frequencies up to 160 MHz

- Nine Selectable Multipliers of the Input Frequency

- Operating Range: VDD = 3.3 V ±10% or 5.0 V ±5%

- Low Jitter Output of 25 ps One Sigma (rms)

- Zero ppm Clock Multiplication Error

- 55% Output Duty Cycle

- TTL/CMOS Output with 25 mA TTL Le